컴퓨터의 경우 논리회로로 구성된다.

이 논리회로의 동작되는 기본이 되는 부울 상수와 그 연산과정, 카르노 맵에 대해 알아본다.

1. 부울 상수와 변수

2. 진리표

3. OR

4. AND

5. NOT

6. NOR

7. NAND

8. NAND / OR 게이트의 범용성

9. 논리회로의 부울대수 표현

10. 논리회로 출력 값 구하기

11. 부울 정리

12. 카르노 맵

13. 논리 게이트의 대안 표시

14. IEEE / ANSI 표준논리 기호

15. 하드웨어 기술언어 ( HDL ) 와 프로그램 언어의 비교

1. 부울 상수와 변수

0과 1 두가지 값만을 가질 수 있다. 실제 숫자가 아닌 전압변수 또는 논리수준이라 하는 전압변수의 상태를 나타낸 것으로, 부울 변수는 연결선 또는 회로의 입출력 단자의 전압 수준에 의해 표현된다.

부울 대수 :

논리회로의 입출력 사이의 관계를 나타내는 방법의 하나로, 두가지 값만을 사용하여 일반대수에 비해 다루기가 쉽다.

0 또는 1의 값만을 가지므로 입력 논리 값은 출력값을 정하는 논리 변수이다. ( 이거 아니면 저거 라는 뜻 )

논리연산 :

OR, AND, NOT 이라는 기본 연산이며 논리게이트 라고 부르는 디지털 회로를 구성한다.

2. 진리표

논리 회로의 출력이 회로의 입력단자에 가해진 논리값에 의해 어떻게 결정되는지 나타내는 방법이다.

N입력 진리표에는 2^N개의 입력 조합이 있다.

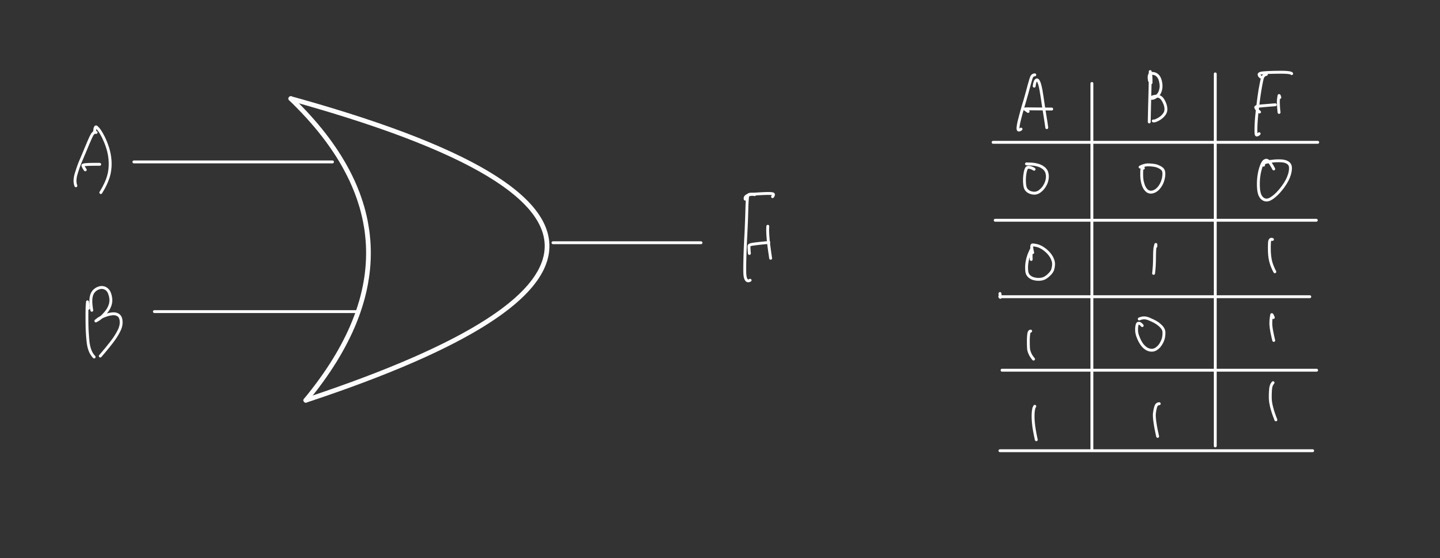

3. OR

OR 연산 :

모두 0이어야 0, 하나라도 1이면 1이다.

x = A+B => x 는 A OR B이다.

OR 게이트 :

2개 이상의 입력을 가지고 출력이 입력의 OR 조합과 같이 동작하게 만든 회로이다.

4. AND

AND 연산 :

하나라도 0이면 0 모두 1이어야 1이다.

x = A·B => x 는 A AND B이다.

AND 게이트 :

2개 이상의 입력을 가지고 출력이 입력의 AND 조합과 같이 동작하게 만든 회로이다.

5. NOT

NOT 연산 :

입력의 반대를 출력한다.

x = A' => x NOT A이다.

NOT 게이트 :

INVERTER 라고도 부른다.

6. NOR

NOR 연산 :

모두 0일때 1, 하나라도 1이면 0

x = (A+B)' => NOR = NOT OR이다.

NOR 게이트 :

2개 이상의 입력을 가지고 출력이 입력의 NOR 조합과 같이 동작하게 만든 회로이다.

7. NAND

NAND :

하나라도 0이면 1, 모두 1이면 0

x = (A·B)' => NAND = NOT AND이다.

NAND 게이트 :

2개 이상의 입력을 가지고 출력이 입력의 NAND 조합과 같이 동작하게 만든 회로이다.

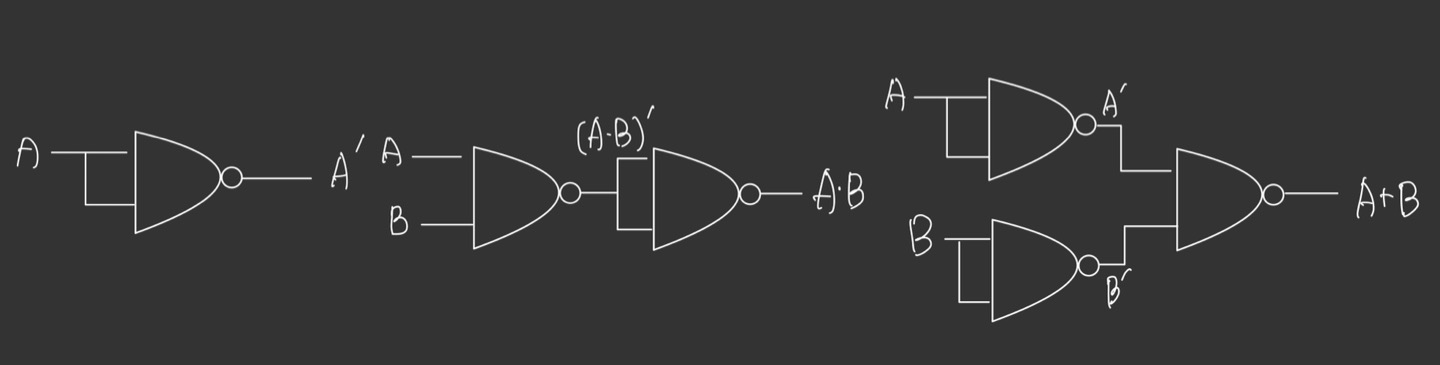

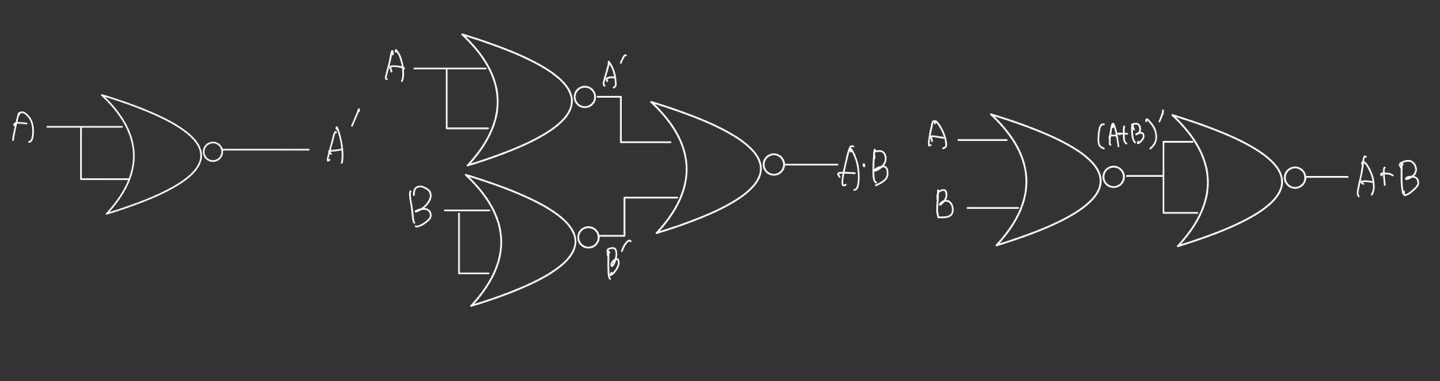

8. NAND / OR 게이트의 범용성

부울연산 표현식의 기본인 OR, AND, NOT의 조합으로 어떤 형식이든 구현이 가능하지만, NAND / NOR 조합만으로도 모든 연산이 가능하다.

| NAND | AND + NOT | NOR | OR + NOT | |

| Delay | 1Δt | 2Δt | 1Δt | 2Δt |

| Size | 1At | 2At | 1At | 2At |

위 표와 같이 OR, AND, NOT의 조합보다 NAND / NOR 조합의 경우가 더 크기도 작고 동작 시간도 적음을 알 수 있다.

회로의 크기가 작아지게 되면 사용하는 전력사용량, 발열이 감소하게 되고 그로인해 제품의 소형화가 가능해 진다.

NAND / NOR 조합의 경우 아래와 같다.

NAND :

NOT : (AA)' = A'

AND : ((AB)'(AB)')' = AB

OR : ((AA)'(BB)')' = A + B

NOR :

NOT : (A + A)' = A'

AND : ((A + A)' + (B + B)')' = AB

OR : ((A + B)' + (A + B)')' = A + B

9. 논리회로의 부울대수 표현

연산 우선순위 :

수학 연산과 같다. 괄호가 · 보다 먼저 계산된다.

10. 논리회로 출력 값 구하기

표를 이용한 분석 :

한번에 1개의 게이트 혹은 논리조합을 분석한다. 이 경우 상호교환 확인이 쉽다.

모든 작업이 끝나면 주어진 논리회로에 고장점을 쉽게 알 수 있다.

각 노드별 출력값을 분석한 후 실제 값과 비교하면 문제가 있는 노드를 알 수 있다.

11. 부울 정리

단변수 정리 :

1. 어떤 변수든 0과 AND 되면 0이다. x·0 = 0

2. 어떤 변수든 1과 AND 되면 변수값과 같다. x·1 = x

3. 어떤 변수든 같은값을 AND하면 변수값과 같다. x·x = x

4. 1번과 같다. x·x' = 0

어떤 값을 넣어도 0이 하나는 생긴다.

5. 어떤 변수든 0과 OR 되면 변수값과 같다. x+0 = x

6. 어떤 변수든 1과 OR 돠면 1이다. x+1 = 1

7. 어떤 변수든 같은값을 AND하면 변수값과 같다. x+x = x

8. 6번과 같다. x+x' = 1

어떤 값을 넣어도 1이 하나는 생긴다.

교환 법칙 :

9. x+y = y+x

10. x·y = y·x

결합 법칙 :

11. x+(y+z) = (x+y) + z = x+y+z

12. x(yz) = (xy)z = xyz

분배법칙 :

13-1. x(y+z) = xy + xz

13-2. (w+x) (y+z) = wy + xy + wz + xz

14. x + xy = x

ㄴ x + xy = x(1+y) = x1= x

ㄴ6 ㄴ2

15. x + x'y = x+y

드모르간의 정리

: 표현식 안의 변수들이 한번만 역변환되는 형태로 바뀔 때까지 계속할 수 있다.

16. (x+y)' = x'y'

17. (xy)' = x' + y'

각 입력에 인버터가 붙은 AND / OR 게이트는 NOR / NAND 게이트와 같다.

12. 카르노 맵

NAND / NOR 게이트의 설명에서 알 수 있듯이 회로가 간소화 될수록 이점이 많다.

부울 식으로 정리를 할 경우 가장 간소화된 형태가 아닐 수 있다.

이경우 입력이 6개 이하의 경우에서 사용이 간편한 카르노 맵을 이용한다. ( 그 이상의 경우 확인이 어렵다. )

규칙 :

입력에 대한 표를 그릴 때 입력이 연속되게 구성한다.

=> 2개의 입력인 경우 : 00 -> 01 -> 10 -> 11 이 아닌, 00 -> 01 -> 11 -> 10 과 같이 하나씩 바꾼다.

표가 구성된 경우 2^N 개씩 사각형을 그린다.

=> 1개, 2개, 4개, 8개 등으로 연속되게 묶는다.

사각형은 최대한 크게 묶는다.

=> 연속된 사각형으로 묶을 수 있는 경우"1개짜리 2개" 가 아닌 "2개짜리 1개"로 묶는다.

사각형은 중복되어 묶을 수 있다.

=> 꼭 중복일 필요는 없지만, 중복으로 사각형이 묶여질 경우 묶어줄 경우 간단해 진다.

표는 위, 아래, 좌, 우, 꼭짓점 끼리 연결 되어 이어져 있다고 생각한다.

-> 아래 설명

1끼리 묶을 경우 곱의 합으로, 0끼리 묶을 경우 합의 곱으로 표현한다.

=> 1끼리 : F = abc + ab'c , 0끼리 : F = (a+b+c)(a+b'+c)

2개 입력 :

3개 입력 :

4개 입력 :

5개 입력 :

6개 입력 :

F = ~~ 꼴의 형태를 카르노 맵으로 바꿀 수도 있지만, 진리표에서 바로 쉽게 표현할 수도 있다.

3개의 입력인 경우 진리표의 크기에 따라서 0~7로 대응 가능하며, 이를 카르노 맵에 대응한다.

1이 적힌 부분을 기준으로 사각형을 그릴 경우 minterm이라 하며 곱의 합이라 하며 시그마( Σ )로 표현한다.

0이 적힌 부분을 기준으로 사각형을 그릴 경우 maxterm이라 하며 합의 곱이라 하며 파이( π )로 표현한다.

이때 minterm 과 maxterm의 개수의 합은 전체 출력 개수와 같다.

13. 논리 게이트의 대안 표시

대안 기호의 처리과정 :

1. 표준 기호의 모든 입출력을 역변환 한다.

2. 연산 기호 AND 와 OR을 맞바꾼다. NOT은 바꾸지 않는다.

활성 논리값 :

방울이 붙어 있으면 LOW, 없으면 HIGH 활성이다.

NAND의 경우 :

논리동작일때 입력은 HIGH, 출력은 LOW ( 모든 입력이 HIGH 일때만 출력이 LOW 이다. )

대안기호일때 입력은 LOW, 출력은 HIGH ( 아무 입력이 LOW이면 출력이 HIGH 이다. )

14. IEEE / ANSI 표준논리 기호

독특한 모양을 가지고 있는 전통적 기호보다 새로운 표준 논리기호로 사각형 기호와 내부의 특별한 의존표현이 소자의 입력 / 출력간의 관계를 나타낸다.

1. 사각형 기호는 논리신호의 역변환을 표시하기 위해 삼각형을 사용한다.

있으면 LOW, 없으면 HIGH이다.

2. 각 사각형 내의 특별표현이 입 / 출력 사이의 논리관계를 나타낸다.

NOT : HIGH 입력 -> LOW 출력

AND (&) : 둘다 HIGH 입력 -> HIGH 출력

OR (>=1) : 1개이상 HIGH 입력 -> HIGH 출력

3. NAND / NOR은 AND / OR 과 진행과정이 같으나 결과값이 반대이다.

15. 하드웨어 기술언어 ( HDL ) 와 프로그램 언어의 비교

하드웨어 기술언어 :

디지털 회로 설계시 표현방법이 컴퓨터로 구현하기 어려워 사용하는 고급 도구

VHDL :

미국 국방성에서 VHSIC 프로그램 설계를 간결하게 문서화 하는 작업을 위한 언어이다.

비트 패턴을 통해 실제소자의 프로그래밍이 가능하며, 어떤 논리회로도 적용이 가능한 범용 언어이다.

AHDL :

알테라 사가 개발였으며 그들의 프로그램 가능 논리소자를 편리하게 구성하기 위해 개발되었다.

배우기는 쉬우나 개발 목적이 목적인 만큼 범용성은 없다.

컴퓨터 프로그램 언어 :

동작속도는 입력의 변화에 대해 출력이 얼마나 빨리 반응할 수 있는지에 달려있다.

모든 입력을 동시에 관찰하여 어떤 변화에도 즉각적으로 반응할 수 있다.

'학과 공부 ( Study ) > 디지털논리회로 ( Digital Logic Circuit )' 카테고리의 다른 글

| 수 체계와 코드 (0) | 2022.04.09 |

|---|---|

| 기초개념 (0) | 2022.04.04 |